CPU结构和功能

本文最后更新于:2020年12月16日 下午

CPU结构和功能

一、CPU的任务

- 取指令:从存储器(register、main-memory、cache)读取指令

- 解释指令:对指令解码,确定要进行的操作

- 取数据:指令的执行可能需要从存储器或I/O中读取数据

- 处理数据:对数据完成要求的算术/逻辑运算

- 写数据:执行的结果可能需要写回存储器或I/O

二、CPU的要求

- CPU能暂时的存储部分数据

- CPU必须知道当前执行指令的位置,以便获取下一条指令的位置

- CPU必须在执行指令期间保存指令和数据

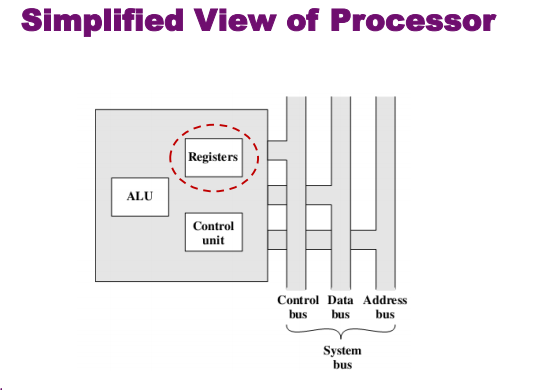

三、寄存器的组成

1. CPU中寄存器主要可以分为两类:

- 用户可见寄存器:允许机器语言或者汇编语言的编程人员通过优化寄存器的使用而减少对内存的访问

- 控制和状态寄存器:由控制器来控制CPU的操作,并由拥有特权的操作系统程序来控制程序的执行

2. 用户可见寄存器:

- 通用寄存器:可被程序员指派各种用途

- 数据寄存器:用于保存数据,不能用于操作数地址的计算

- 地址寄存器:用于可以是自身有某种通用性或者专用性的寻址方式

- 标志寄存器:保存条件码、允许程序员读出,但不能更改

3. 寄存器的设计出发点:

- 使用完全通用寄存器还是规定各寄存器的用途

- 寄存器的数量

- 寄存器的长度

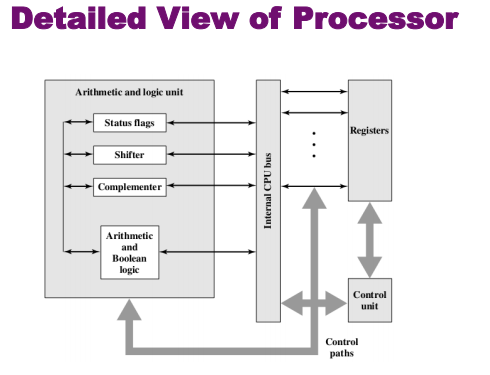

4. 控制和状态寄存器:

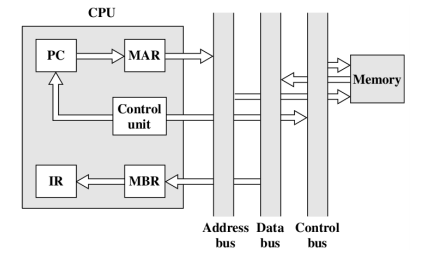

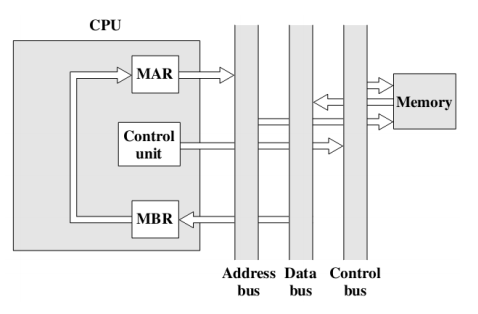

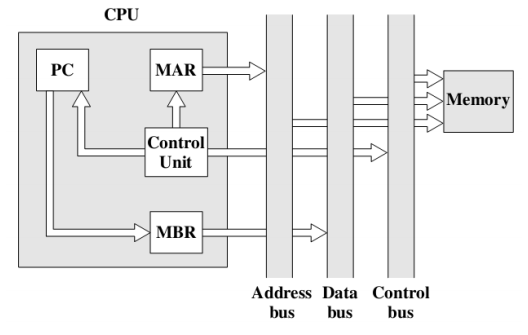

- 程序计数器(PC):存放待取指令的地址

- 指令寄存器(IR):存放最近取来的地址

- 存储器地址寄存器(MAR):存放存储器位置的地址

- 存储器缓冲寄存器(MBR):存有将被写入或最近从存储器读出的字

5. 程序状态字(PSW):

- 符号(sign):容纳算术运算结果的符号位

- 零(zero):当结果是0时置位

- 进位(carry):操作导致向最高位有向上进位或借位时被置位

- 等于(equal):逻辑结果相等置位

- 溢出(overflow):用于指示算术运算溢出

- 中断允许/禁止(interrupt enable/disable):用于允许/禁止中断

- 监管(supervisor):指出CPU是执行在监管模式还是用户模式

6. 设计控制和状态寄存器组织时考虑的几个因素:

- 考虑对操作系统的支持(某些控制信息专门为控制操作系统使用)

- 考虑控制信息在寄存器和存储器之间的分配

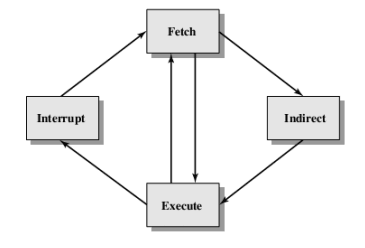

7. 指令周期:

- 取指:将下一条指令从存储器中读入CPU

- 执行;解释操作码并完成指定操作

- 中断:如果中断允许并且有中断发生,则保存当前状态执行中断

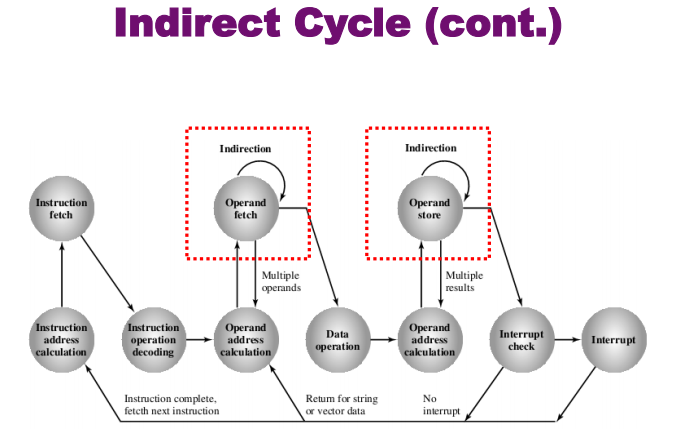

8. 间接周期:

- 指令的执行可能涉及到内存中的一个或多个操作数,并且每个操作数都需要内存访问

- 如果使用间接地址,需要额外的内存访问

- 将间接地址的获取视为一个或多个指令周期

9. 数据流:

-

- 控制器向PC发送请求 -> PC将存有的下一条指令的地址传给MAR -> MAR放到地址总线上

- 控制器将控制信号放到控制总线上 -> 存储器接收信号 -> 存储器获取指令地址并将对应的指令放到数据总线上

- MBR从数据总线上获取指令然后传给IR

-

-

MBR存储的是指令的地址 -> MBR将地址传给MAR -> MAR将该地址传放到地址总线上

-

控制器将控制信号放到控制总线上 -> 存储器接收信号并读取指令的地址

-

存储器根据地址将对应指令放到数据线上 -> MBR读取指令

- 控制器向MAR传送信号 -> MAR将当前数据要保存到的地址放到地址总线上

- 控制器向PC传送信号 -> PC将当前要保存的数据传入MBR -> MBR将数据放到数据总线上

- 控制器向控制总线上发送信号 -> 存储器读取信号 -> 存储器从地址总线上接收地址,并从数据总线上接收数据

- 存储器将数据写入对应的地址

-

四、指令流水线技术:

1. 流水线技术:把制作过程安排在一条装配线上,多个产品能在各个阶段同时被加工

2. 对指令执行使用流水线技术:显然能够加快指令的执行,但是使得执行速度翻倍是不可能的,原因如下:

- 执行时间一般长于指令的执行(执行指令和取指令都可能使用I/O,所以会产生冲突,一次只能有一个进行)

- 条件分支指令使得待取的下一条指令的地址未知(当多条指令执行了一些步骤后,遇到跳转指令,这些指令执行的步骤将会作废)

3.对指令执行的细分(为了进一步加速):

- 取指:获取下一条要执行指令到MBR

- 译码:解析指令,确定操作码、操作数

- 计算操作数:计算源操作数的有效地址

- 取操作数:从存储器中读取操作数(寄存器中的数据不需要读取)

- 执行:完成指定操作

- 写回操作数:将结果写回存储器

4. 几个限制性能提升的因素:

- 细分的各个阶段时间不完全相等

- 遇到条件转移指令时,之前进行的指令会作废

- 寄存器和存储器可能产生冲突

5. 人们认为流水线中阶段越多,执行速度越快?No

- 流水线的每一阶段,都会有某些开销设计数据在MBR间的传送,以及各种准备会使得一次指令的总的执行时间边长

- 优化流水线的使用和处理存储器及寄存器相关性所需要的控制逻辑总量,会随着流水线阶段数的增长而急剧增长

- 锁存延迟,即流水线阶段之间的缓冲需要一定时间来完成其操作,这也会增加指令周期的时间

6.流水线性能:

- $t_{i}$:流水线第$i$段的延迟

- $t_{m}$:最大段延迟

- $k$:指令流水线段数

- $d$:所存延迟

- $t = max[ t_{i} ] + d = t_{m} + d$ -> $t$: 指令流水线周期

- 假设$n$条指令没有条件转移的在进行,$T_{k, n} = [ k + (n - 1)] t$表示k段流水线执行n条指令所需的总时间

- 完成第一条指令需要k个周期,其余n-1条指令需要n-1个周期

- 加速比$S_{k} = T_{1, n} / T_{k, n} = nk / (k + n - 1)$

本博客所有文章除特别声明外,均采用 CC BY-SA 4.0 协议 ,转载请注明出处!